▌本文在幹嘛

生成式AI (如ChatGPT、Gemini)可以提高工程師的生產力,國內IC設計大廠聯發科也積極導入生成式AI「達哥DaVinci」來提昇IC設計工程師們的生產力。

按照此趨勢,未來很有機會每個IC設計工程師都會和ChatGPT一起合作開發晶片,早日學會怎麼跟生成式AI合作才能提高工作競爭力。

筆者身為電機系和數位IC設計領域的一份子,在網路上找不到評測ChatGPT在生成HDL (Verilog、VHDL)時會遇到什麼困難,所以我們決定跳下來自己評測。

ChatGPT真的已經搶走IC設計工程師的工作了嗎?該怎麼跟ChatGPT溝通互動?怎麼叫ChatGPT一步到位生出能用的程式碼?這些都是我們認為待解的重要挑戰。

因此,我準備了五個數位IC設計的代表性題目,由簡入難來測試ChatGPT的IC設計實力。

希望幫前輩、同行、同學先踩過一些坑,拋磚引玉,與社群一起增強用ChatGPT合作開發IC時的詠唱實力 (Prompting)。

▌測試項目

我們由簡而難精選五題測試,題目參考自Stanford Advanced VLSI Circuit Design課程,以及清大邏輯設計實驗、IC Lab、DSP IC設計、計算機算數等課程內的作業。

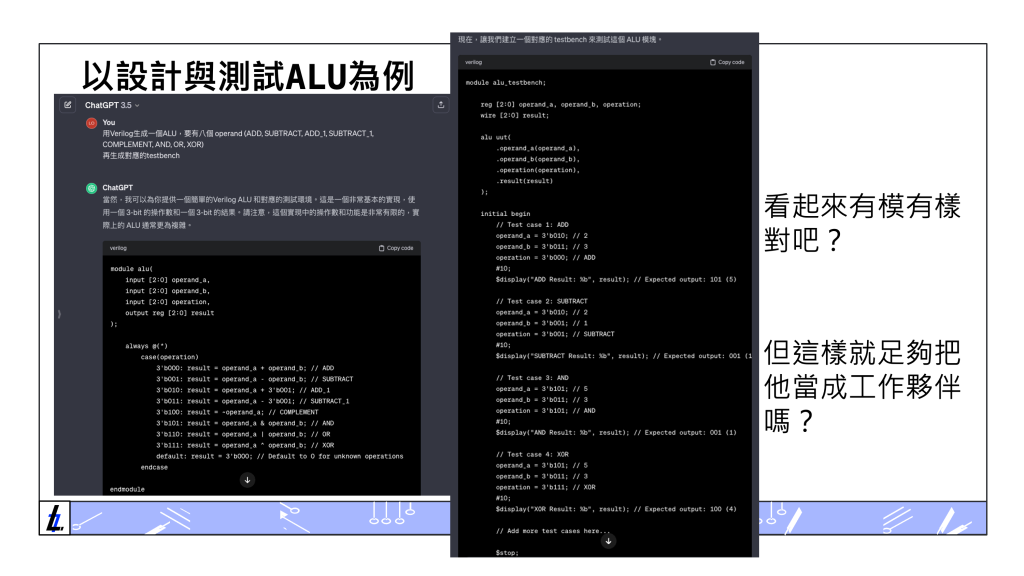

每題都要求ChatGPT要用Verilog寫出電路與對應的testbench,這兩個任務都是身為一個數位IC設計工程師在前端流程一定會做到的事情。

五題分別為:

Q1. 計數器設計與驗證 (Counter)

Q2. 算術邏輯單元的設計與驗證 (8-operand ALU)

Q3. 有線脈衝響應處理器設計與驗證 (FIR Digital Filter Processor)

Q4. 16×16有號數布斯乘法器 (16×16 Signed Booth Multiplier using type-0 adder)

Q5. 2×2脈動陣列設計與驗證 (2×2 Systolic Array)

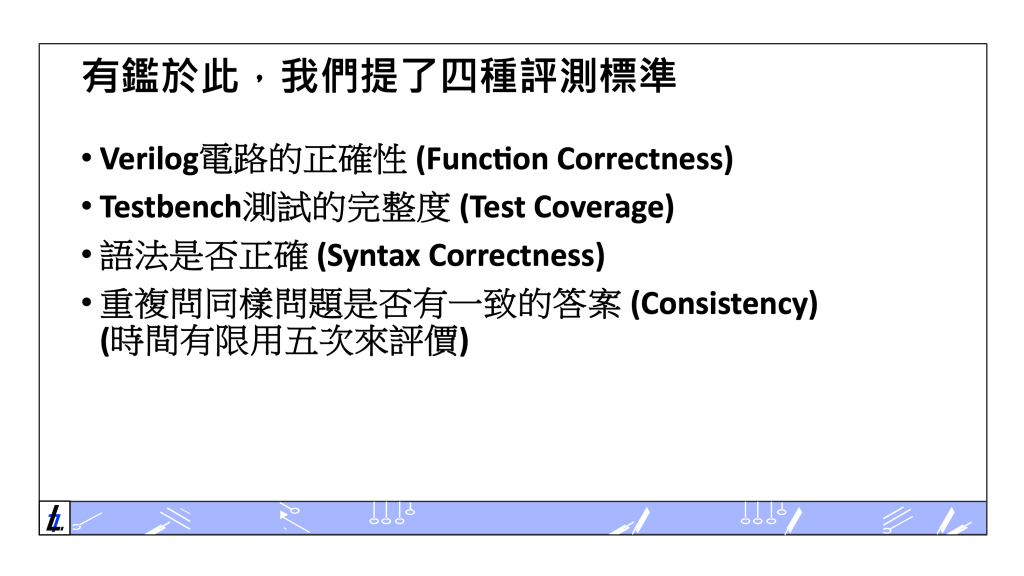

▌如何評分

評分有4個項目,最低一顆星,最高5顆星,評分項目分別為:

C1. Verilog電路的正確性 (Function Correctness)

C2. Testbench測試的完整度 (Test Coverage)

C3. 語法是否正確 (Syntax Correctness)

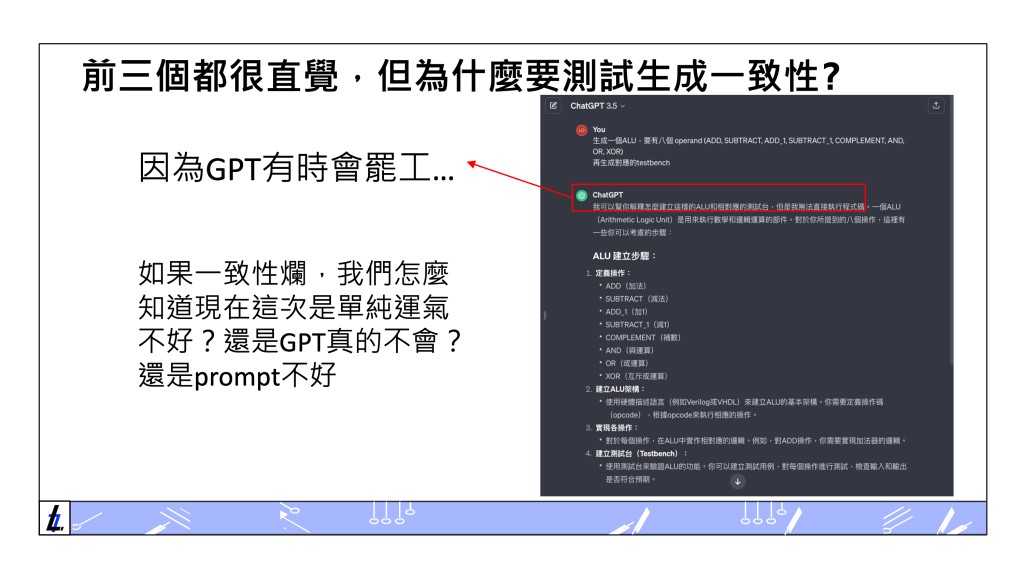

C4. 重複問同樣問題是否有一致的答案 (Consistency) (因筆者時間有限,用五次來評價)

▌ChatGPT (GPT-3.5) 評測表現 (2023年12月評測)

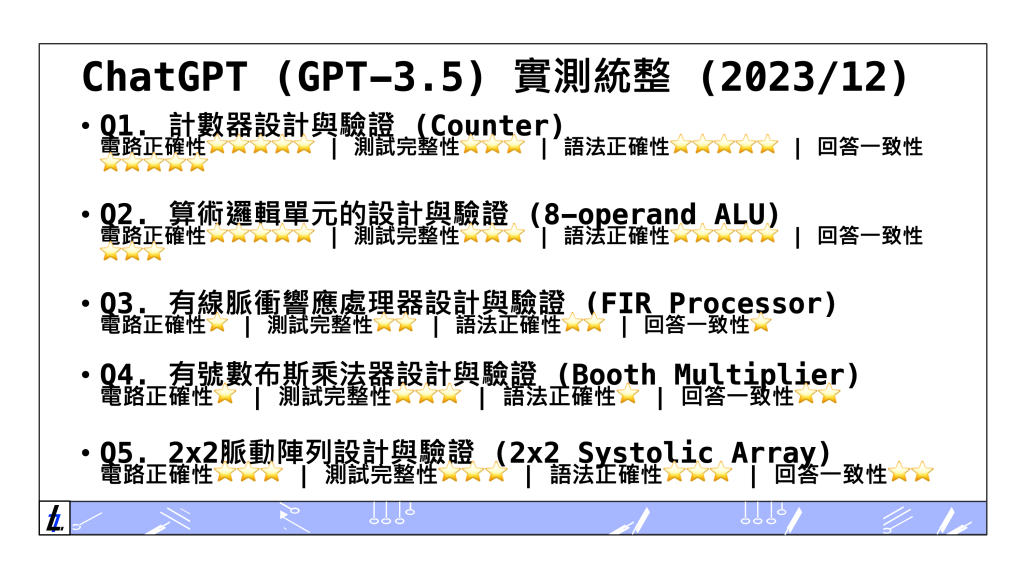

Q1. 計數器設計與驗證 (Counter)

電路正確性⭐️⭐️⭐️⭐️⭐️ | 測試完整性⭐️⭐️⭐️ | 語法正確性⭐️⭐️⭐️⭐️⭐️ | 回答一制性⭐️⭐️⭐️⭐️⭐️

Q2. 算術邏輯單元的設計與驗證 (8-operand ALU)

電路正確性⭐️⭐️⭐️⭐️⭐️ | 測試完整性⭐️⭐️⭐️ | 語法正確性⭐️⭐️⭐️⭐️⭐️ | 回答一制性⭐️⭐️⭐️

Q3. 有線脈衝響應處理器設計與驗證 (FIR Digital Filter Processor)

電路正確性⭐️ | 測試完整性⭐️⭐️ | 語法正確性⭐️⭐️ | 回答一制性⭐️

Q4. 16×16有號數布斯乘法器設計與驗證 (16×16 Signed Booth Multiplier using type-0 adder)

電路正確性⭐️ | 測試完整性⭐️⭐️⭐️ | 語法正確性⭐️ | 回答一制性⭐️⭐️

Q5. 2×2脈動陣列設計與驗證 (2×2 Systolic Array)

電路正確性⭐️⭐️⭐️ | 測試完整性⭐️⭐️⭐️ | 語法正確性⭐️⭐️⭐️ | 回答一制性⭐️⭐️

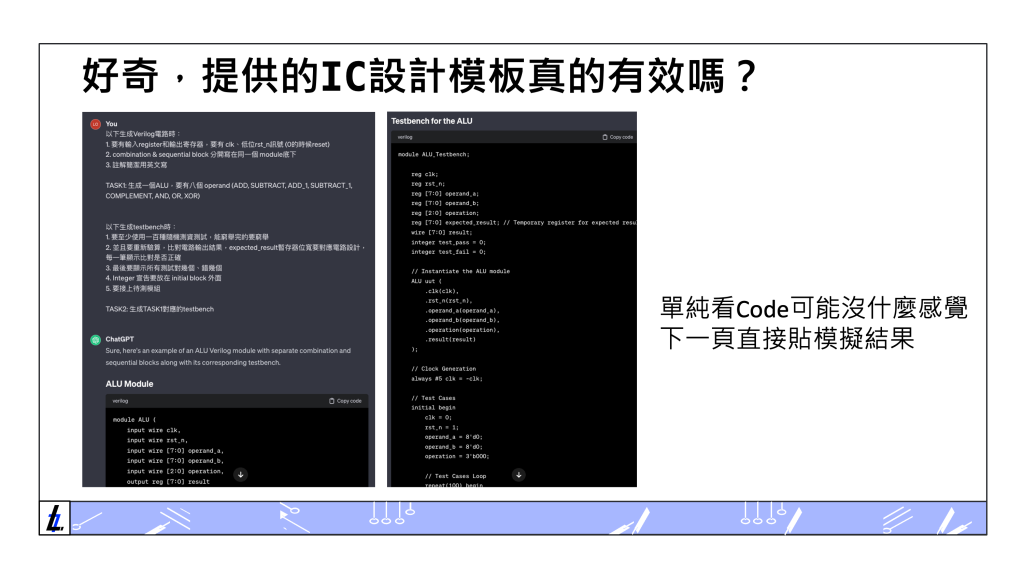

▌IC設計工程師專屬的 Prompt模板

經過這週每天和ChatGPT朝夕相處,我們把踩過的坑都整理成下面的詠唱模板,實測產生Verilog的品質真的好了很多:

以下生成Verilog電路時:

– 要有輸入register和輸出寄存器,要有 clk、低位rst_n訊號 (0的時候reset)

– combination & sequential block 分開寫在同一個 module底下

– 註解簡潔用英文寫

– Integer不準宣告在 for迴圈中,像 for (int i = 0; i < 32; i = i + 1)就是錯誤的寫法

– Integer變數要宣告在always block外面

– 矩陣初始值要一行一行寫,不要寫成一個 list 或 array assignment,要全部寫出來

– 只能用 always block來寫,不准用initial begin

– reg 宣告不能用assign賦值

TASK1: 用Verilog生成一個ALU,要有八個 operand (ADD, SUBTRACT, ADD_1, SUBTRACT_1, COMPLEMENT, AND, OR, XOR)

以下生成testbench時:

– 測試的Coverage要高,至少使用一百種隨機測資測試,能窮舉完的要窮舉

– 並且要在testbench內用Verilog重新驗算,比對電路輸出結果,expected_result暫存器位寬要對應電路設計,每一筆顯示比對是否正確

– 最後要顯示所有測試對幾個、錯幾個

– Integer 要宣告在 initial block 外面

– 要接上待測模組

TASK2: 生成TASK1對應的testbench

但距離幫上工程師大忙仍然有一大段路要走,也歡迎大家試試看,跟我們分享屬於你的數位IC設計詠唱模板。

▌我們是誰

蘿蔔實驗室 – 與你分享晶片設計實用知識

Facebook: LoboLab 蘿蔔實驗室

IG: lobolab.semiconductor

歡迎到我們的IG看詳細實測,真的覺得蠻好玩的!歡迎追蹤!

註:IC為 integrated circuit的縮寫,也就是大眾熟知的電路